Архитектура RISC-V (Никита Ермаков, OSSDEVCONF-2019)

Материал из 0x1.tv

- Докладчик

- Никита Ермаков

RISC-V это гибкая, модульная архитектура набора команд (ISA) с открытой лицензией Creative Commons Attribution 4.0 International. Существуют как FPGA, так и ASIC (например HiFive Unleashed, Kendryte K210) реализации архитектуры. В данной работе приведён обзор архитектуры RISC-V, программной экосистемы, а также текущие результаты портирования ALT на RISC-V (rv64gc).

Содержание

Видео

Презентация

Thesis

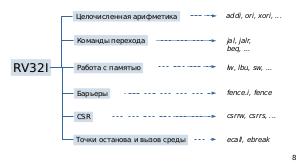

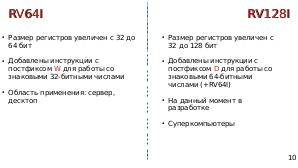

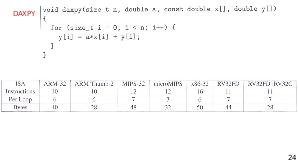

RISC-V [1] это новая, гибкая, модульная, little-endian архитектура набора команд (ISA), имеющая открытую лицензию Creative Commons Attribution 4.0 International (CC BY 4.0). Летом 2010 года была начата работа над первой версией ISA, которая уже осенью того же года использовалась в курсе по дизайну интегральных схем университета Беркли [2]. Первая версия ISA была опубликована под BSD лицензией и была предназначена для образовательных и академических целей. В августе 2014 года на конференции HotChips-26[3] состоялась первая публичная демонстрация архитектуры RISC-V. На конференции были показаны ядра Rocket[4] и Hwacha[5]. Позже, в 2015 году, был основан фонд RISC-V Foundation, а в 2018 году Linux Foundationи RISC-V Foundation объявили о сотрудничестве с целью ускорения open source разработки и адаптации RISC-V ISA. На данный момент RISC-V Foundation включает в себя более 325 участников. Основу архитектуры RISC-V составляет базовая целочисленная (integer) ISA, которая должна присутствовать в любой реализации процессора плюс одно или несколько расширений. Базовая целочисленная ISA представляет собой минимальный набор инструкций необходимых для компиляторов, ассемблеров, компоновщиков и операционных систем и включает в себя инструкции для записи, сохранения, переходов и целочисленной арифметики. Существует четыре варианта базовой целочисленной ISA: RV32I, RV64I, RV32E и RV128I. Каждый вариант характеризуется шириной целочисленных регистров и размером пользовательского адресного пространства. Первые два варианта отвечают 32-х и 64-х битному адресному пространству соответственно. Аппаратные и программные (ОС) реализации могут обеспечивать как два этих типа ISA сразу (RV32I и RV64I), так и один из них. RV32E представляет собой уменьшенную копию RV32I разработанную для embedded систем. Было обнаружено, что в минимальных дизайнах ядер RV32I верхняя половина регистров (x16-x31) занимает четверть общей площади кристалла (за исключением памяти). Цена за один кристалл зависит от его площади, как , где – его площадь[6][7]. Уменьшение числа регистров позволяет снизить стоимость ядра и его энергопотребление, что критично для микроконтроллеров и embedded систем. Основные отличия RV32E от RV32I:

- уменьшен размер регистров с 32 до 16;

- регистры счётчиков циклов, выполненных инструкций и таймера больше не являются обязательными для реализации.

RV128I является расширением RV64I на 128-ми битное адресное пространство так же, как и RV64I является расширением RV32I на 64-х битное адресное пространство. На данный момент RV128I не завершена и может быть изменена, когда появится первое реальное использование 128-ми битного, плоского, адресного пространства.

Помимо базовой целочисленной ISA, существуют различные расширения:

- M — умножение и деление целых чисел;

- A — атомарные операции;

- F — число с плавающей запятой одинарной точности;

- D — число с плавающей запятой двойной точности;

- Q — число с плавающей запятой четверной точности;

- L — десятичная плавающая точка;

- C — сжатые 16-битные инструкции;

- V — векторные инструкции;

- B — инструкции для манипуляций с битами;

- J — динамически транслируемые языки (например Java). ISA будет поддерживать динамические проверки и сборщик мусора;

- T — транзакционная память;

- P — упакованные SIMD инструкции;

- N — прерывания уровня пользователя.

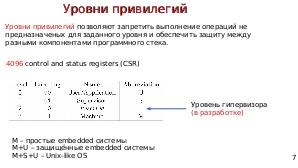

На данный момент завершены следующие ISA: RV32/64I, M, A, F, D, Q, C. Набор расширений IMAFD для краткости обозначают одной буквой G (General). Варианты RISC-V со спецификацией RV32/64GC являются совместимыми с ОС на базе ядра Linux. Описанные выше модули относятся к пользовательскому уровню ISA. В произвольный момент времени, ядро RISC-V работает на определённом уровне привилегий. На данный момент определены три уровня привилегий в которых может находиться ядро RISC-V, в порядке увеличения привилегий: пользовательский (U), супервизора (S) и машинный (M). Уровни привилегий используются для защиты между разными компонентами программного стека. Попытка выполнения операций не предусмотренных данным уровнем привилегий приведёт к возникновению исключения. Машинный уровень (M) имеет наивысшие привилегии и является обязательным для реализации в любом ядре RISC-V[8]. Уровни пользователя и супервизора предназначены для пользовательских приложений и операционных систем соответственно. Текущий уровень привилегии ядра RISC-V кодируется двумя битами, что позволяет закодировать 4 значения уровня. Одно из значений зарезервировано для уровня гипервизора, который находятся в разработке.

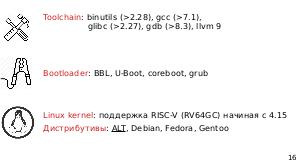

Среди разработчиков программного обеспечения идёт активное освоение новой архитектуры. Ядро Linux начиная с версии 4.15 имеет поддержку архитектуры RISC-V, а начиная с версии 4.19 содержит все необходимые драйверы для загрузки системы в QEMU. Тулчейн получил поддержку RISC-V начиная с версий gcc 7.1, binutils 2.28, glibc 2.27, gdb 8.3.

Среди загрузчиков на данный момент доступны GRUB, U-Boot, Berkeley bootloader.

Разработчики операционных систем на базе ядра Linux активно портируют их на RISC-V. Существуют порты ALT, Debian, Fedora, Gentoo.

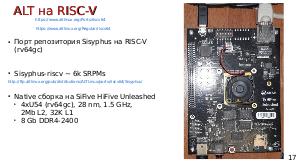

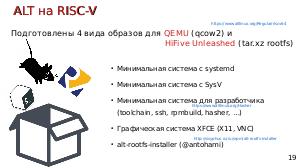

Порт ALT на RISC-V (rv64gc) построен вокруг репозитория Sisyphus. На данный момент порт репозитория Sisyphus насчитывает более 5700 исходных RPM пакетов опубликованных в открытом доступе. Сборка осуществляется в нативном режиме на плате HiFive Unleashed. Для обеспечения воспроизводимой и безопасной сборки используется hasher. Порт ALT на RISC-V имеет несколько вариантов образов системы:

- Минимальная система с systemd;

- Минимальная система с SysV;

- Минимальная система для разработчика (rpmbuild, hasher, gcc);

- Графическая система с XFCE (X11, VNC).

Каждый из вариантов доступен как для QEMU, так и для системы на кристалле (SoC) HiFive Unleashed.

Примечания и ссылки

- ↑ The RISC-V Instruction Set Manual Volume I: User-Level ISA, https://riscv.org/specifications/

- ↑ Krste A. Instruction Sets Should Be Free: The Case For RISC-V / Krste Asanović и David A. Patterson // EECS Department, University of California, Berkeley. — 2014.

- ↑ RISC-V на HotChips-26, https://riscv.org/2014/08/risc-v-at-hotchips-26/

- ↑ Ядро Rocket RISC-V, https://www.lowrisc.org/docs/tagged-memory-v0.1/rocket-core/

- ↑ Ядро Hwacha RISC-V, http://hwacha.org/

- ↑ John H. Computer Architecture: A Quantitative Approach / John L. Hennessy и David A. Patterson // ISBN: 978-0-12-383872-8. — 2012.

- ↑ David P, The RISC-V Reader: An Open Architecture Atlas / David A. Patterson и Andrew Waterman // ISBN: 978-0-99-924911-6. — 2017.

- ↑ The RISC-V Instruction Set Manual Volume II: Privileged Architecture, https://riscv.org/specifications/privileged-isa/

Plays:536 Comments:1