Открытая архитектура RISC-V (Никита Ермаков, OSSDEVCONF-2018)

Материал из 0x1.tv

- Докладчик

- Никита Ермаков

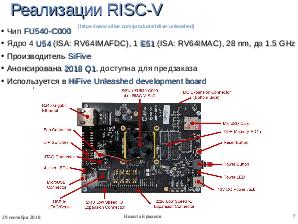

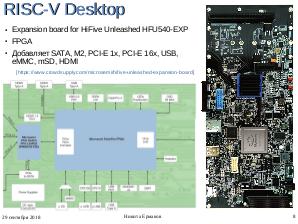

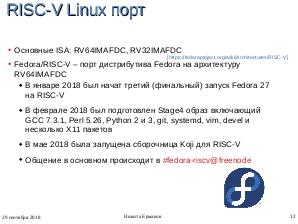

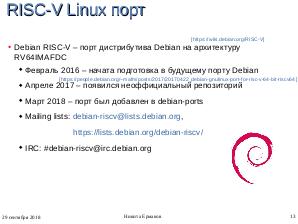

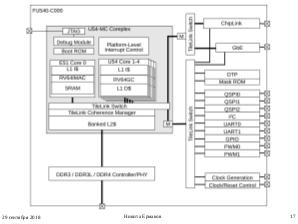

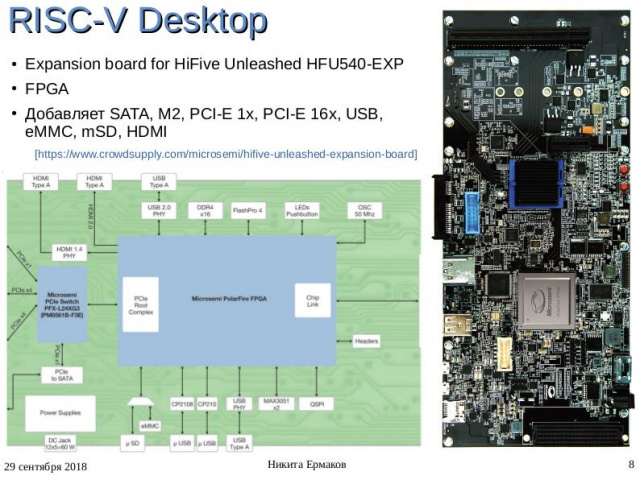

RISC-V является архитектурой с открытым набором команд (ISA) основанной на принципах компьютера с сокращённым набором команд (RISC). На данный момент существует несколько реализаций RISC-V, например системы на кристалле (SoC) от компании SiFive. Среди разработчиков операционных систем (ОС) на базе ядра Linux, таких как Red Hat, ALT, Fedora, Debian, начат процесс портирования ОС на RISC-V.

В данном докладе приведены текущие успехи, а также дальнейшие планы, по портированию ALT на RISC-V.

Содержание

Видео

Посмотрели доклад? Понравился? Напишите комментарий! Не согласны? Тем более напишите.

Презентация

Thesis

Архитектура набора команд (ISA) это спецификация по инструкциям или машинному коду которые передаются в процессор, а также другие детали о том, как работает данное семейство процессоров. Современные ISA это огромные и сложные документы, но что более важно, большинство ISA имеют патенты и агрессивные авторские права. Например если некто решил независимо реализовать ARM процессор, ему потребуется понести расходы связанные с лицензиями.

Открытые ISA, среди которых которых RISC-V, напротив имеют пермиссивные лицензии. Например, спецификации RISC-V имеют лицензию Creative Commons license (CC BY 4.0), все инструкции RISC-V свободны от патентов. Помимо RISC-V существуют другие открытые ISA, например OpenSPARC, OpenRISC. Проект OpenSPARC был начат корпорацией Sun Microsystems в 2005 году, были открыты спецификации процессора UltraSPARC T1 и T2. На данный момент дизайн OpenSPARC является устаревшим. Другой проект OpenRISC берёт своё начало в 2000 году. На сегодняшний день существует единственная версия архитектуры OpenRISC 1000 (or1k), которая описывает семейство 32-х и 64-х битных процессоров имеющих опциональные расширения такие, как поддержка векторных операций и чисел с плавающей запятой. В 2011 году ядро Linux 3.1 получило поддержку OpenRISC и в 2014 году появился порт Debian. Однако в 2016 году порт Debian закрылся вследствие проблем с авторскими правами. Активность по изменению кода ядра связанного с OpenRISC замедлилась.

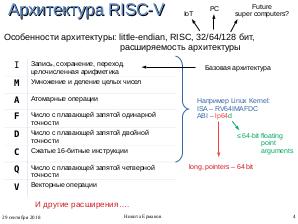

RISC-V является little-endian архитектурой. Одна из главных особенностей архитектуры RISC-V это её расширяемость, что позволяет создавать разнообразные реализации. Минимальная спецификация архитектуры RISC-V включает в себя только инструкции для записи, сохранения, переходов и целочисленной арифметики. Код инструкций не зависит от размера регистра, минимальная спецификация обозначается RV32I, RV64I или RV128I для размеров операнда 4, 8 или 16 байт соответственно. Существуют различные расширения, некоторые из них:

- M — умножение и деление целых чисел;

- A — атомарные операции;

- F — число с плавающей запятой одинарной точности;

- D — число с плавающей запятой двойной точности;

- Q — число с плавающей запятой четверной точности;

- L — десятичная плавающая точка;

- C — сжатые 16-битные инструкции.

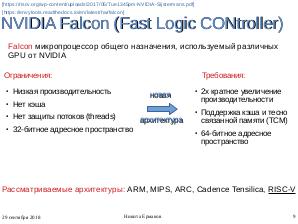

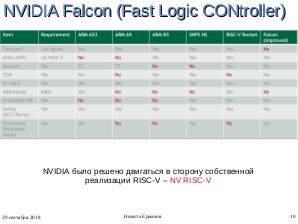

Большинство Linux совместимых чипов имеют спецификации RV32IMAFDC или RV64IMAFDC. Среди разработчиков операционных систем на базе ядра Linux, таких как Red Hat, ALT, Gentoo, Fedora, Debian идёт активный процесс портирования ОС на RISC-V. Крупные компании также заинтересованы в использовании RISC-V. Например, NVIDIA планирует использовать RISC-V для замены процессора Falcon на графических картах GeForce, компания Western Digital планирует использовать RISC-V в своих будущих проектах. Таким образом архитектура RISC-V заполучила большое внимание рынка ИТ и является перспективной открытой технологией которая, возможно, позволит человечеству продвинуться вперёд на пути к открытости аппаратной начинки наших устройств.

Примечания и ссылки

Plays:2450 Comments:13