Конвейерные схемы, вычисляющие несколько выражений (Борис Штейнберг, SECR-2018) — различия между версиями

Материал из 0x1.tv

StasFomin (обсуждение | вклад) |

StasFomin (обсуждение | вклад) |

||

[[File:{{#setmainimage:Конвейерные схемы, вычисляющие несколько выражений (Борис Штейнберг, SECR-2018)!.jpg}}|center|640px]]

{{LinksSection}}

* [https://2018.secrus.org/program/submitted-presentations/pipeline-circuits-to-compute-several-expressions/ Talks page on SECR site]

<!-- <blockquote>[©]</blockquote> -->

{{fblink|2243831929203149}}

{{vklink|1388}}

<references/>

<!-- topub -->

{{stats|disqus_comments=0|refresh_time=2020-01-22T2228T15:2203:40.584117437413|vimeo_plays=1|youtube_comments=0|youtube_plays=26}}

[[Категория:SECR-2018]]

[[Категория:Алгоритмы]]

[[Категория:Параллельное программирование]]

[[Категория:Компиляторы]] | |||

Версия 12:03, 28 января 2020

- Докладчик

- Борис Штейнберг

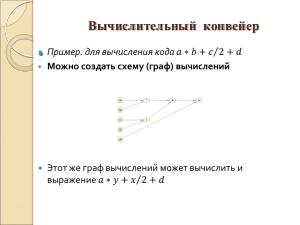

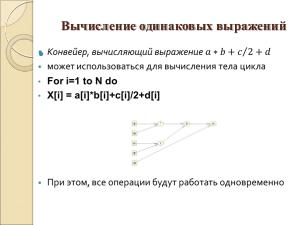

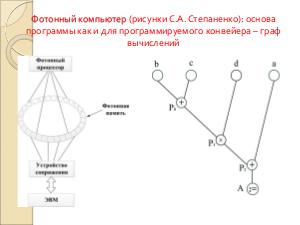

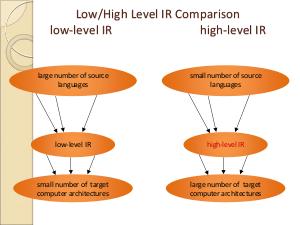

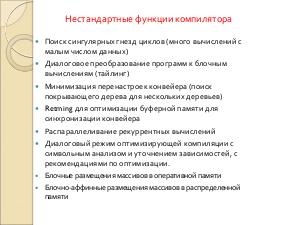

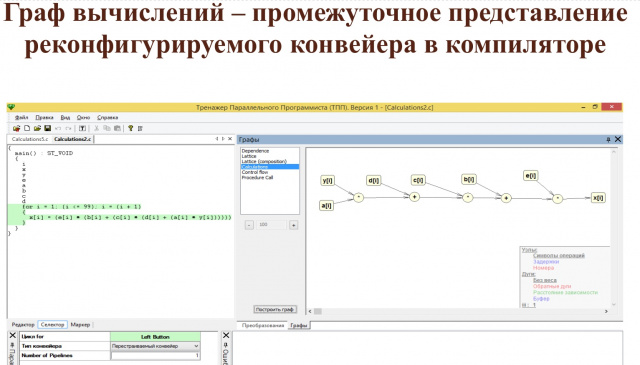

Данная статья относится к области высокоуровневого синтеза. Работа посвящена предварительным преобразованиям программ языка Си, до их автоматического преобразования компилятором в HDL-описание соответствующей электронной схемы. Рассматриваемые преобразования направлены на поиск такой конвейерной схемы, которая способна вычислять несколько различных программных циклов. Создание такого конвейерного вычислителя может привести к экономии ресурсов ПЛИС при генерации схемы и может сэкономить время, необходимое для перепрограммирования ПЛИС-ускорителя. Реализация таких преобразований предполагается на основе ОРС (оптимизирующей распараллеливающей системы).

Задача поиска оптимального конвейера оказывается вычислительно сложной, но, в некоторых частных случаях, сводится к известной задаче выравнивания строк.

Видео

Посмотрели доклад? Понравился? Напишите комментарий! Не согласны? Тем более напишите.

Презентация

Примечания и ссылки

Plays:27 Comments:0